AI時代芯片設(shè)計變革 軟件定義硬件的深度演進

隨著人工智能技術(shù)的飛速發(fā)展,尤其是以生成式AI為代表的大模型應(yīng)用崛起,傳統(tǒng)芯片設(shè)計模式正面臨前所未有的挑戰(zhàn)。在AI驅(qū)動的時代,芯片設(shè)計已不再僅僅是硬件工程師的專屬領(lǐng)域,而是需要與軟件設(shè)計與開發(fā)深度融合,甚至由軟件來定義硬件的一場深度變革。

一、AI對芯片設(shè)計的核心挑戰(zhàn)

當(dāng)前,AI應(yīng)用對算力的需求呈指數(shù)級增長,且呈現(xiàn)出高度動態(tài)化、多樣化的特點。傳統(tǒng)通用處理器(如CPU)在能效比和專用計算效率上難以滿足要求,而定制化AI芯片(如ASIC、NPU)雖然性能優(yōu)越,但設(shè)計周期長、靈活性不足,難以跟上AI算法快速迭代的步伐。這種矛盾催生了芯片設(shè)計范式的轉(zhuǎn)變:從“硬件先行,軟件適配”轉(zhuǎn)向“軟件定義,硬件協(xié)同”。

二、軟件設(shè)計與開發(fā)成為芯片創(chuàng)新的驅(qū)動力

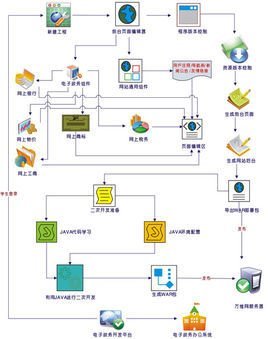

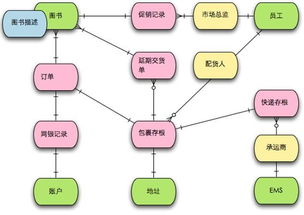

在AI時代,芯片設(shè)計的起點越來越多地源自軟件需求。開發(fā)者需要針對特定AI工作負載(如Transformer推理、擴散模型訓(xùn)練)進行深度優(yōu)化,這就要求芯片架構(gòu)能夠靈活響應(yīng)軟件定義的計算圖、內(nèi)存訪問模式和精度要求。因此,現(xiàn)代芯片設(shè)計流程中,軟件仿真、建模和編譯器技術(shù)變得至關(guān)重要。

例如,通過高級綜合(HLS)工具,軟件工程師可以用C++或Python等高級語言描述算法,自動生成硬件描述代碼,大幅縮短設(shè)計周期。開源指令集架構(gòu)(如RISC-V)的興起,使得軟件生態(tài)能夠更深入地影響硬件設(shè)計,實現(xiàn)定制化擴展指令,以加速AI計算。

三、軟硬件協(xié)同設(shè)計的深度變革

這場變革的核心在于打破軟硬件之間的壁壘,實現(xiàn)全棧優(yōu)化。具體體現(xiàn)在:

- 架構(gòu)創(chuàng)新:芯片設(shè)計需支持可重構(gòu)計算(如FPGA與ASIC融合),允許硬件資源根據(jù)軟件需求動態(tài)配置,以平衡效率與靈活性。

- 工具鏈演進:從EDA工具到AI驅(qū)動的設(shè)計自動化,軟件工具能夠預(yù)測芯片性能、功耗和面積,并自動優(yōu)化布局布線,甚至生成設(shè)計代碼。

- 生態(tài)共建:芯片成功不再僅依賴硬件指標(biāo),而是需要構(gòu)建從底層驅(qū)動、編譯器到框架(如PyTorch、TensorFlow)的完整軟件棧,降低開發(fā)者的使用門檻。

四、未來展望:走向“Chip as a Service”

隨著云原生和邊緣計算的發(fā)展,芯片設(shè)計可能進一步演變?yōu)榉?wù)化模式。軟件開發(fā)者通過API調(diào)用異構(gòu)算力,而底層硬件則根據(jù)全局負載動態(tài)重構(gòu)。例如,通過Chiplet技術(shù)和先進封裝,將不同功能的計算單元(如AI加速、內(nèi)存、I/O)模塊化組合,由軟件調(diào)度實現(xiàn)最優(yōu)資源配置。

AI時代呼喚芯片設(shè)計與軟件開發(fā)的深度交融。這場變革不僅是技術(shù)的升級,更是思維的重塑——芯片將逐漸成為軟件可編程、可定義的智能載體。只有擁抱軟硬件協(xié)同創(chuàng)新,才能在未來算力競爭中占據(jù)先機,賦能千行百業(yè)的智能化轉(zhuǎn)型。

如若轉(zhuǎn)載,請注明出處:http://www.zahf.cn/product/44.html

更新時間:2026-03-09 10:58:57